# T2R2 東京科学大学 リサーチリポジトリ Science Tokyo Research Repository

## 論文 / 著書情報 Article / Book Information

| 題目(和文)            |                                                                                                                                                                                                |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title(English)    | Hardware-Accelerated Modeling of Large-Scale Networks-on-Chip                                                                                                                                  |

| 著者(和文)            | Chu Van Thiem                                                                                                                                                                                  |

| Author(English)   | Thiem Van Chu                                                                                                                                                                                  |

| 出典(和文)            | 学位:博士(工学),<br>学位授与機関:東京工業大学,<br>報告番号:甲第10994号,<br>授与年月日:2018年9月20日,<br>学位の種別:課程博士,<br>審査員:吉瀬 謙二,横田 治夫,宮﨑 純,渡部 卓雄,金子 晴彦                                                                         |

| Citation(English) | Degree:Doctor (Engineering),<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:甲第10994号,<br>Conferred date:2018/9/20,<br>Degree Type:Course doctor,<br>Examiner:,,,, |

|                   | 博士論文                                                                                                                                                                                           |

| Type(English)     | Doctoral Thesis                                                                                                                                                                                |

# Hardware-Accelerated Modeling of Large-Scale Networks-on-Chip

by

#### Thiem Van Chu

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Engineering

Department of Computer Science Graduate School of Information Science and Engineering Tokyo Institute of Technology

© Thiem Van Chu 2018. All rights reserved.

## **Abstract**

Networks-on-Chip (NoCs) are becoming increasingly important elements in different types of computing hardware platforms, from general-purpose many-core processors for supercomputers and datacenters to application-specific MultiProcessor Systems-on-Chip (MPSoCs) for embedded applications. They are also integral parts of many emerging accelerators for critically essential applications such as deep neural networks, databases, and graph processing. In such a hardware platform, the NoC is responsible for connecting the other components together and thus has a significant impact on the overall performance. To achieve higher performance and better power efficiency, many-core processors with more and more cores have been developed. For the similar reason and to meet the increasingly stringent requirements of target applications, the number of processing elements, memory and input/output modules integrated on an MPSoC/accelerator is increasing. As the number of components that need to be interconnected increases, the overall performance becomes highly sensitive to the NoC performance. Therefore, research and development of NoCs play a key role in designing future large-scale architectures with hundreds to thousands of components.

A major obstacle to research and development of large-scale NoCs is the lack of fast modeling methodologies that can provide a high degree of accuracy. Analytical models are extremely fast but may incur significant inaccuracy in many cases. Thus, NoC designers often rely on simulation to test their ideas and make design decisions. Unfortunately, while being much more accurate than analytical modeling, conventional software simulators are too slow to simulate large-scale NoCs with hundreds to thousands of nodes in a reasonable time. Because of this, most studies are limited to NoCs with around 100 nodes. To address the simulation speed problem, there have been some attempts to build NoC emulators using Field-Programmable Gate Arrays (FPGAs). However, these NoC emulators suffer from the scalability problem. They cannot scale to large NoCs due to the FPGA logic and memory constraints. A recent study has shown that even an extremely large FPGA does not have enough logic blocks to fit a moderately complex NoC design of around 150 nodes. What is even worse is that emulating a large-scale NoC also requires a large amount of memory for modeling of traffic workloads. However, the on-chip memory capacity of an FPGA is very small, at most from several to around only ten megabytes. Off-chip memory

(usually DRAM) has a larger capacity but is much slower than on-chip memory. The use of off-chip memory may substantially degrade the emulation speed.

This dissertation proposes methods for fast and accurate modeling of NoCs with up to thousands of nodes by FPGA emulation with cycle accuracy, an extremely high degree of emulation accuracy in which target NoCs are emulated on a cycle-by-cycle basis. While the goal of these methods is to enable fast and accurate modeling of large-scale NoCs, they are also beneficial to the modeling of current NoCs with tens to around 100 nodes.

To overcome the FPGA logic constraints, the dissertation proposes a novel use of time-division multiplexing (TDM) where the emulation cycle is decoupled from the FPGA cycle and a network is emulated by time-multiplexing a small number of nodes. This approach makes it possible to emulate NoCs with up to thousands of nodes using a single FPGA. The dissertation focuses on applying the TDM technique to two commonly used network topologies, two-dimensional (2D) mesh and fat-tree (k-ary n-tree), which are the bases of almost all actually constructed network topologies. It thus can be expected that the proposed methods can be extended for a wide range of networks.

While the time-division multiplexing methods enable the emulation of large-scale NoCs, they alone are not sufficient. To achieve a high emulation speed, it is essential to address the memory constraints caused by modeling traffic workloads.

There are two types of workloads used in NoC emulation: synthetic workloads and trace-driven workloads. Synthetic workloads are those based on mathematical modeling of common traffic patterns in real applications. They have a high degree of flexibility and are easy to create. A set of carefully designed synthetic workloads can provide a relatively thorough coverage of the characteristics of the target NoCs. It has also been shown that evaluation on synthetic workloads is indispensable in many cases. For instance, when designing a routing algorithm, the use of synthetic workloads is mandatory for assessing the algorithm on possible corner cases like those under extremely high loads. On the other hand, trace-driven workloads are those based on trace data captured from either a working system or an execution-driven simulation/emulation. They are effective for evaluating target NoCs under the intended applications.

Currently, due to the lack of trace data of large-scale NoC-based systems, using synthetic workloads is practically the only feasible approach for emulating large-scale NoCs with thousands of nodes. To overcome the memory constraints caused by modeling synthetic workloads, the dissertation proposes a method to reduce the amount of required memory so that it is not necessary to use off-chip memory even when emulating NoCs with thousands of nodes. This method not only makes the overall design much simpler but also significantly contributes to the improvement of emulation speed. It and the proposed time-multiplexed emulation methods enable a NoC emulator which can be used to model a mesh-based NoC with 16,384 nodes (128×128 NoC) and a fat-tree-based NoC with 6,144 switch nodes and 4,096 terminal nodes (4-ary 6-tree NoC) and

is up to three orders of magnitude faster than a widely used cycle-accurate software simulator while providing the same results.

The dissertation shows the usability of the developed emulator by designing and modeling an effective routing algorithm for 2D mesh NoCs and evaluating it for various network sizes, from 8×8 to 128×64. The proposed routing algorithm has an oblivious routing scheme and thus a low design complexity. It, however, can achieve high performance by properly distributing the load over two network dimensions and using an efficient deadlock avoidance method. Because of the lack of fast modeling methodologies that can provide a high degree of accuracy, most existing routing algorithms have been evaluated in NoCs of limited size. The developed FPGA-based NoC emulator enables the evaluation in large-scale NoCs with thousands of nodes in a practical time. The evaluation results show that, in the currently common NoC sizes of around 100 nodes, the proposed algorithm significantly outperforms other popular oblivious routing algorithms and can provide comparable performance to a complicated adaptive routing algorithm. However, as the NoC size increases, the performance of the algorithms is strongly affected by the resource allocation policy in the network and the effects are different for each algorithm. This result would not be obtained if modeling of large-scale NoCs could not be performed.

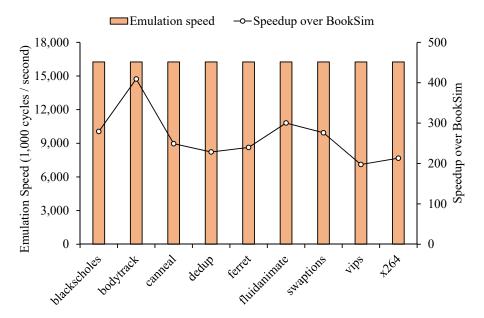

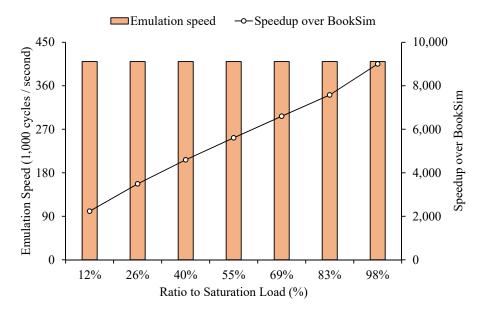

While synthetic workloads can provide a relatively thorough coverage of the characteristics of the emulated NoCs, evaluation on trace-driven workloads is still required in some cases such as assessing some application-specific optimizations. The dissertation takes this into account and extends the proposed NoC emulator to support trace-driven emulation which will be useful for research and development of large-scale NoCs in the future when trace data of large-scale NoC-based systems are available. Since trace data are large, they must be stored in off-chip memory. The dissertation proposes an effective trace data loading architecture and some methods to hide the off-chip memory access time and improve the scalability of the emulation architecture in terms of operating frequency and logic requirements. These proposals are tightly coupled to the time-multiplexed emulation methods. The evaluation results show that the extended NoC emulator is two orders of magnitude faster than the above-mentioned software simulator when emulating an  $8\times8$  NoC with the widely used PARSEC traces while also providing the same results; and the speedup is increased to three orders of magnitude when emulating a  $64\times64$  NoC with trace data created based on a synthetic workload.

The work in this dissertation contributes directly to the formation of infrastructures for research and development of large-scale NoCs, which is crucial for developing more powerful and efficient many-core processors, MPSoCs, and hardware accelerators in the future.

## Acknowledgment

The work presented in this thesis would not have been possible without the help and support of so many people to whom I owe a lot of gratitude.

First and foremost, I would like to thank my advisor, Associate Professor Kenji Kise, who has given me this great opportunity to come and work with him at Tokyo Tech. He taught me how to do good research and effectively communicate my ideas to others. He also generously provided the resources and the comfortable environment that enabled me to pursue my ideas to fruition. His passion, hard work, and dedication to the success of his students are truly inspiring. I could not wish for a better advisor.

I would like to thank Professor Haruo Yokota, Professor Jun Miyazaki, Professor Takuo Watanabe, and Associate Professor Haruhiko Kaneko for serving on my defense. Their comments and feedback on the thesis were immensely helpful.

I would also like to thank Assistant Professor Shimpei Sato for his advice and inspiration. He always encouraged me to explore and challenge further. It has been a pleasure to collaborate and co-author with him. I will miss our mid-night discussions.

I am grateful to Ryosuke Sasakawa for proposing the original idea from which I developed the LEF routing algorithm in this thesis. I also would like to thank Shi FA and Myeonggu Kang for their contributions in the development of the LEF routing algorithm.

I was fortunate to have had an opportunity to work together with Professor Tomohiro Yoneda at the National Institute of Informatics and Professor Masashi Imai at Hirosaki University in the project of comparing synchronous and asynchronous Networks-on-Chip. They provided valuable feedback and perspective on my work. This experience makes me feel that doing research with researchers with different perspectives is an extremely good opportunity to enhance my ability.

I would like to thank all the former and current members of my research laboratory. I would like to give special thanks to Associate Professor Shinya Takamaeda-Yamazaki, Assistant Professor Ryohei Kobayashi, Susumu Mashimo, and Tomohiro Misono. Associate Professor Shinya Takamaeda-Yamazaki has made valuable comments on my work. Assistant Professor Ryohei Kobayashi has helped me a lot since I first came to the laboratory. I really enjoyed discussing with Susumu Mashimo. We had great times at two conferences, FCCM 2017 and MICRO 2017,

in the United States. He and Tomohiro Misono also carefully reviewed my written Japanese.

I would like to thank Yukiko Asoh and the other assistants in our department for handling all the administrative duties that made things run smoothly for all the students. My abroad business trips would not be possible without them.

I would like to acknowledge the Japan Society for the Promotion of Science for providing the generous funding that supported my work.

I am so blessed to have had truly good friends to lean on in both good and bad times. Thank you, Giang, Viet, Nam, and Quang Anh, for always being there for me.

Finally, I would like to express my gratitude to my family. Their love, support, and encouragement have been an important part of my study at Tokyo Tech.

## **Contents**

| 1 | Intr | oductio | n                                                                     | 1  |

|---|------|---------|-----------------------------------------------------------------------|----|

|   | 1.1  | Motiva  | ation                                                                 | 1  |

|   |      | 1.1.1   | The Advent of New Computing Architectures                             | 1  |

|   |      | 1.1.2   | Interconnection Problems                                              | 3  |

|   |      |         | 1.1.2.1 Problems of Traditional On-Chip Interconnection Architectures | 3  |

|   |      |         | 1.1.2.2 Network-on-Chip (NoC)                                         | 4  |

|   |      | 1.1.3   | Challenges in NoC Design                                              | 5  |

|   | 1.2  | Thesis  | Contributions                                                         | 7  |

|   | 1.3  | Thesis  | Organization                                                          | 10 |

| 2 | Bacl | kground | d and Related Work                                                    | 11 |

|   | 2.1  | NoC B   | Basics                                                                | 11 |

|   |      | 2.1.1   | Topology                                                              | 11 |

|   |      | 2.1.2   | Routing                                                               | 12 |

|   |      | 2.1.3   | Flow Control                                                          | 14 |

|   |      | 2.1.4   | Router Architecture                                                   | 14 |

|   | 2.2  | FPGA    | Basics                                                                | 15 |

|   | 2.3  | NoC N   | Modeling                                                              | 16 |

|   |      | 2.3.1   | Analytical Modeling                                                   | 16 |

|   |      | 2.3.2   | Hardware Prototyping                                                  | 17 |

|   |      | 2.3.3   | Simulation                                                            | 18 |

|   |      |         | 2.3.3.1 Simulation Methodologies                                      | 18 |

|   |      |         | 2.3.3.2 Cycle Accuracy                                                | 18 |

|   |      | 2.3.4   | The Need for Simulation Acceleration                                  | 19 |

|   |      | 2.3.5   | FPGA Emulation: A Hardware-Accelerated Approach to Simulation         | 20 |

|   | 2.4  | Relate  | d Work                                                                | 20 |

|   |      | 2.4.1   | Software Simulators                                                   | 20 |

|   |      | 2.4.2   | FPGA-Based Emulators                                                  | 21 |

|   | 2.5 | NoC E   | Emulation Model                                                        | 24 |

|---|-----|---------|------------------------------------------------------------------------|----|

|   |     | 2.5.1   | Basic Components                                                       | 24 |

|   |     |         | 2.5.1.1 Router                                                         | 25 |

|   |     |         | 2.5.1.2 Traffic Generator                                              | 25 |

|   |     |         | 2.5.1.3 Traffic Receptor                                               | 26 |

|   |     | 2.5.2   | Flit Model                                                             | 27 |

| 3 | Nov | el Time | -Division Multiplexing Methods                                         | 29 |

|   | 3.1 | Introdu | uction                                                                 | 29 |

|   | 3.2 | High-I  | Level Datapath for Emulating 2D Meshes                                 | 30 |

|   | 3.3 | High-I  | Level Datapath for Emulating k-Ary n-Trees                             | 31 |

|   | 3.4 | Inter-C | Cluster/Router Emulation Buffers                                       | 33 |

|   |     | 3.4.1   | Essential Characteristic for Efficient Mapping to BRAMs                | 33 |

|   |     | 3.4.2   | 2D Mesh                                                                | 34 |

|   |     | 3.4.3   | k-Ary n-Tree                                                           | 34 |

|   |     |         | 3.4.3.1 Using Logical Port IDs instead of Physical Port IDs            | 34 |

|   |     |         | 3.4.3.2 Procedure for Calculating Logical Port IDs                     | 35 |

|   |     |         | 3.4.3.3 Conversion between Logical Port IDs and Physical Port IDs      | 37 |

|   |     | 3.4.4   | Proof of Correctness of the Procedure for Calculating Logical Port IDs |    |

|   |     |         | in k-Ary n-Trees                                                       | 40 |

|   |     |         | 3.4.4.1 Connection of Routers in a k-Ary n-Tree                        | 40 |

|   |     |         | 3.4.4.2 Proof                                                          | 42 |

|   | 3.5 | Detaile | ed Timing                                                              | 57 |

|   |     | 3.5.1   | 2D Mesh                                                                | 57 |

|   |     | 3.5.2   | k-Ary n-Tree                                                           | 59 |

|   | 3.6 | Emula   | tion Code Translation                                                  | 59 |

|   |     | 3.6.1   | Register                                                               |    |

|   |     | 3.6.2   | Memory                                                                 |    |

|   | 3.7 | Summ    | ary                                                                    | 62 |

| 4 | FNo | C: An l | Emulator for NoC Emulation under Synthetic Workloads                   | 63 |

|   | 4.1 | Introdu | uction                                                                 | 63 |

|   | 4.2 | Efficie | nt Method for Modeling of Synthetic Workloads                          | 66 |

|   | 4.3 | Evalua  | ation                                                                  | 69 |

|   |     | 4.3.1   | Resource Requirements                                                  | 71 |

|   |     | 4.3.2   | Emulation Accuracy                                                     | 72 |

|   |     | 133     | Emulation Performance                                                  | 73 |

|   |     | 4.3.4   | Comparison with other FPGA-Based NoC Emulators              | 76         |

|---|-----|---------|-------------------------------------------------------------|------------|

|   | 4.4 | Summ    | ary                                                         | 78         |

| 5 | A U | se Case | of FNoC in Design and Modeling of a New Routing Algorithm   | <b>7</b> 9 |

|   | 5.1 | Introdu | uction                                                      | 79         |

|   | 5.2 | The Ll  | EF Routing Algorithm                                        | 83         |

|   |     | 5.2.1   | Selection of XY DOR and YX DOR                              | 83         |

|   |     | 5.2.2   | Deadlock Avoidance                                          | 84         |

|   |     |         | 5.2.2.1 Proposed Deadlock Avoidance Method                  | 85         |

|   |     |         | 5.2.2.2 Proof of Deadlock Freedom                           | 87         |

|   |     | 5.2.3   | Optimization on the Selection of XY DOR and YX DOR          | 90         |

|   |     | 5.2.4   | LEF Implementation                                          | 92         |

|   | 5.3 | Evalua  | ution                                                       | 92         |

|   |     | 5.3.1   | Evaluation Methodology                                      | 92         |

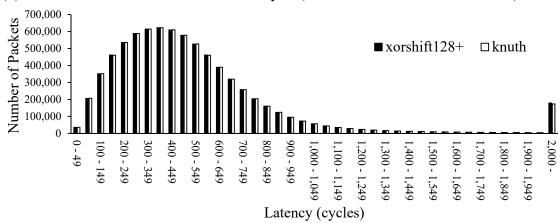

|   |     | 5.3.2   | LEF Performance                                             | 94         |

|   |     |         | 5.3.2.1 Middle-Scale NoCs                                   | 94         |

|   |     |         | 5.3.2.2 Large-Scale NoCs                                    | 97         |

|   |     | 5.3.3   | The Effectiveness of the Proposed Deadlock Avoidance Method | 99         |

|   | 5.4 | Summ    | ary                                                         | 00         |

| 6 | Tow | ards No | oC Emulation under Trace-Driven Workloads                   | 102        |

|   | 6.1 | Introdu | uction                                                      | 02         |

|   | 6.2 | Backg   | round                                                       | 04         |

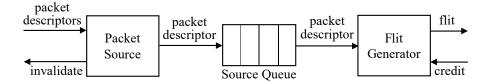

|   |     | 6.2.1   | Traffic Generator Architecture                              | 04         |

|   |     | 6.2.2   | Time-Multiplexed Emulation                                  | 05         |

|   | 6.3 | Propos  | sed Trace-Driven Emulation Architecture                     | 06         |

|   |     | 6.3.1   | Architecture Overview                                       | 06         |

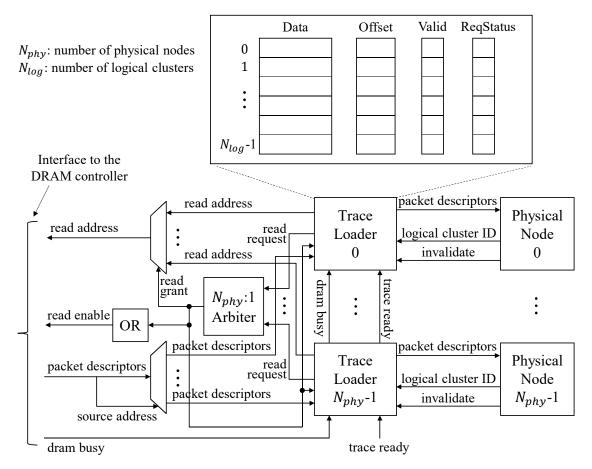

|   |     | 6.3.2   | Trace Loader Architecture                                   | 07         |

|   |     | 6.3.3   | Emulation Methodology                                       | 10         |

|   | 6.4 | Evalua  | ntion                                                       | 11         |

|   |     | 6.4.1   | Emulation Accuracy                                          | 12         |

|   |     | 6.4.2   | Resource Requirements and Scalability                       | 13         |

|   |     | 6.4.3   | Emulation Performance                                       | 14         |

|   |     | 6.4.4   | Comparison with other FPGA-Based NoC Emulators              | 18         |

|   | 6.5 | Summ    | arv 1                                                       | 20         |

| 7 | Con | clusions and Future Work | 121 |

|---|-----|--------------------------|-----|

|   | 7.1 | Conclusions              | 121 |

|   | 7.2 | Future Work              | 123 |

# **List of Figures**

| 1.1 | Growth in processor performance from 1978 to 2017 (Figure adapted from [1]).                |    |

|-----|---------------------------------------------------------------------------------------------|----|

|     | The data are collected by running the SPEC integer benchmarks [2] and normal-               |    |

|     | ized to the performance of the VAX-11/780 [3]                                               | 2  |

| 1.2 | An example of a many-core processor architecture with 2D-mesh-based NoC                     | 4  |

| 2.1 | The position of routers (R), cores (C), and links between routers in each of the            |    |

|     | two network topologies studied in this thesis.                                              | 12 |

| 2.2 | The conventional input-queued VC router architecture with credit-based flow                 |    |

|     | control [4]                                                                                 | 15 |

| 2.3 | Simulation speed of BookSim [5], one of the most widely used cycle-accurate                 |    |

|     | NoC simulators, for different network sizes                                                 | 19 |

| 2.4 | Emulation models of direct and indirect networks                                            | 24 |

| 2.5 | Architecture of each traffic generator and traffic receptor                                 | 26 |

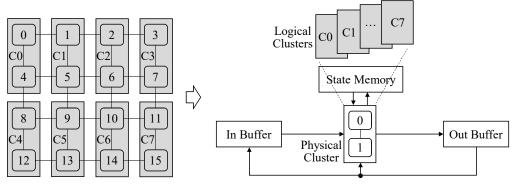

| 3.1 | Emulating 2D mesh networks: (a) a 4×4 mesh NoC is emulated using two phys-                  |    |

|     | ical nodes and (b) high-level datapath                                                      | 30 |

| 3.2 | Emulating $k$ -ary $n$ -trees: (a) a 2-ary 3-tree is emulated by time-multiplexing 12       |    |

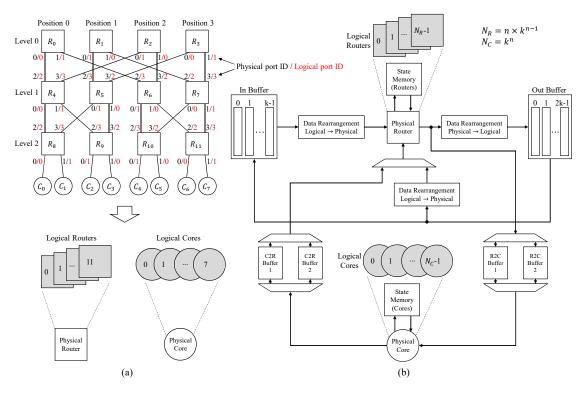

|     | logical routers and 8 logical cores; (b) high-level datapath                                | 32 |

| 3.3 | Every router in a torus has the same port mapping function and this function is             |    |

|     | bijective                                                                                   | 34 |

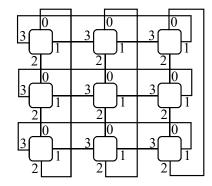

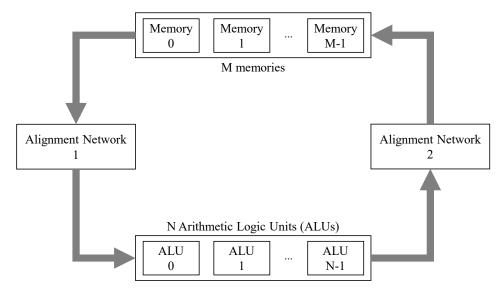

| 3.4 | An array processor [6]                                                                      | 38 |

| 3.5 | (a) A $4\times4$ array of data. (b) An example of distributing the $4\times4$ array of data |    |

|     | in figure (a) to eight memories in an array processor with four ALUs so that any            |    |

|     | row, any column, any $2\times2$ square block, the forward diagonal, and the backward        |    |

|     | diagonal can be accessed without conflicts                                                  | 38 |

| 3.6  | (a) Inter-router communication data in the emulation of a 2-ary 3-tree (Figure                                       |    |

|------|----------------------------------------------------------------------------------------------------------------------|----|

|      | 3.2(a)): $d_r^p$ indicates the output data of physical port $p$ of router $r$ ; the output                           |    |

|      | and input data of router $R_4$ (output data: $d_4^0$ , $d_4^1$ , $d_4^2$ , $d_4^3$ ; input data: $d_0^0$ , $d_2^0$ , |    |

|      | $d_8^2$ , $d_9^2$ ) are highlighted in green and red, respectively. (b) Read conflicts are                           |    |

|      | avoided by dividing the out buffer and the in buffer into multiple smaller buffer                                    |    |

|      | memories according to the logical port ID instead of the physical port ID: buffer                                    |    |

|      | i ( $i = 0; 1; 2; 3$ ) stores output data of logical port $i$ of the routers                                         | 39 |

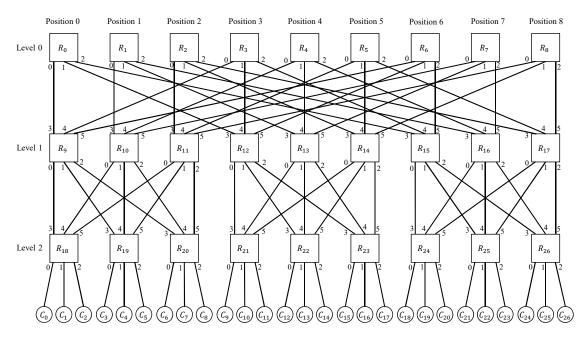

| 3.7  | $k$ -ary $n$ -tree with physical port ID assignment. A 3-ary 3-tree consists of $k^n =$                              |    |

|      | $3^3 = 27$ cores connected by $n = 3$ levels of $k^{n-1} = 3^{3-1} = 9$ radix-2 $k$ (radix-6)                        |    |

|      | routers. The levels are consecutively numbered starting from 0 at the root up to                                     |    |

|      | the leaves. The routers in each level are numbered from 0 at the leftmost position                                   |    |

|      | to $k^{n-1}-1=3^{3-1}-1=8$ at the rightmost position. In each router, the physical                                   |    |

|      | IDs of the down ports are from 0 at the leftmost position to $k-1=3-1=2$                                             |    |

|      | at the rightmost position while the physical IDs of the up ports are from $k=3$ at                                   |    |

|      | the leftmost position to $2k-1=2\times 3-1=5$ at the rightmost position                                              | 41 |

| 3.8  | k-ary $n$ -tree (3-ary 3-tree) with logical port ID assignment. The logical port ID                                  |    |

|      | assignment of a router may be different from that of another                                                         | 42 |

| 3.9  | (a) Datapath between the state memory and the physical cluster in time-multiple-                                     |    |

|      | xed emulation of 2D meshes. (b) Timing diagram: $S^i_j$ and $d^i_j$ are the state and the                            |    |

|      | outgoing data respectively of logical cluster $j$ after emulation cycle $i-1$ ; both                                 |    |

|      | $S^i_j$ and $d^i_j$ are used at emulation cycle $i$                                                                  | 57 |

| 3.10 | Translating from (a) the original RTL code to (b) the time-multiplexed emulation                                     |    |

|      | RTL code                                                                                                             | 60 |

| 3.11 | Preprocessing before the code translation: a register array in (a) is converted to                                   |    |

|      | the standard form in (b).                                                                                            | 61 |

| 4.1  | Pseudo-code for simulating each packet source and the corresponding source                                           |    |

|      | queue with Bernoulli process in BookSim. This code is executed every simula-                                         |    |

|      | tion cycle                                                                                                           | 64 |

| 4.2  | Timeline of the network and a packet source. The enqueue process describes how                                       |    |

|      | the packet source generates and injects packet descriptors into the source queue                                     |    |

|      | while the dequeue process describes how packet descriptors are ejected from the                                      |    |

|      | source queue by the network. The state of the source queue is determined by                                          |    |

|      | both the network's time and the packet source's time                                                                 | 66 |

| 4.3 | The state transition diagrams of each packet source and the network in the conventional method and the proposed method for modeling synthetic workloads. |     |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | Here, packet source i and its corresponding source queue are denoted by PS <sub>i</sub> and                                                              |     |

|     | SQ <sub>i</sub> , respectively. The current time counters of packet source i and the network                                                             |     |

|     | are denoted by $t_i$ and $t$ , respectively                                                                                                              | 68  |

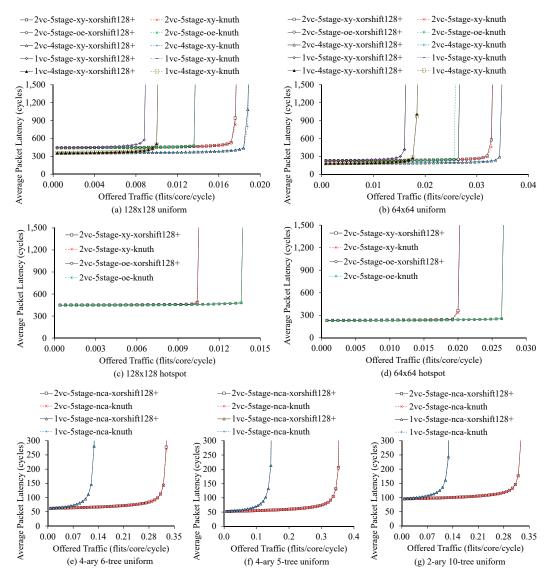

| 4.4 | Average packet latency: emulating 16 target NoCs with the parameters described                                                                           |     |

|     | in Tables 4.1 and 4.2.                                                                                                                                   | 73  |

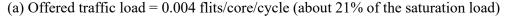

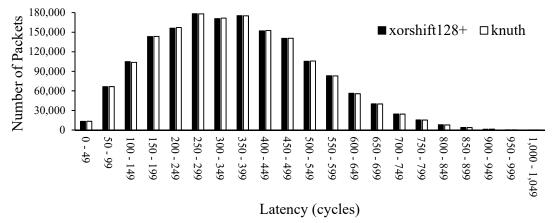

| 4.5 | Distributions of packet latency: emulating the 128×128-2vc-4stage-xy (detailed                                                                           | 75  |

| 1.5 | parameters are described in Tables 4.1 and 4.2) under uniform traffic                                                                                    | 74  |

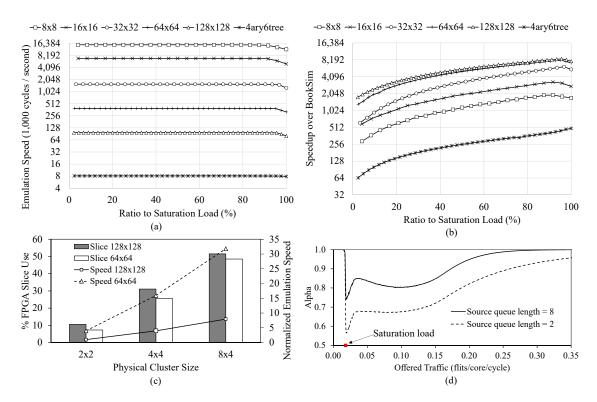

| 4.6 | (a) FNoC's emulation speed for different network sizes; (b) FNoC's speedup over                                                                          | , . |

|     | BookSim; (c) FNoC's normalized emulation speed versus % FPGA slice use for                                                                               |     |

|     | different physical cluster sizes; (d) The stalling effect coefficient $\alpha$ with different                                                            |     |

|     | traffic loads and source queue lengths in the case of emulating the 128×128-2vc-                                                                         |     |

|     | 5stage-xy                                                                                                                                                | 75  |

|     | 2                                                                                                                                                        |     |

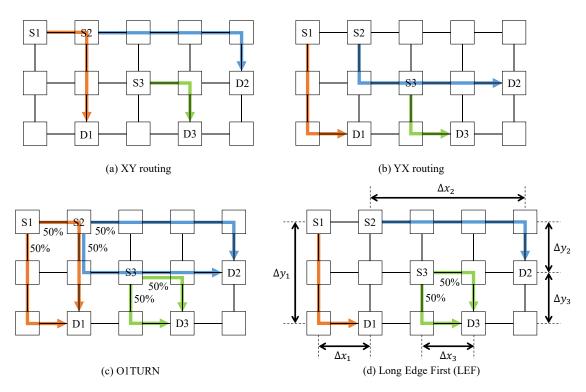

| 5.1 | (a) XY DOR: packets are routed first in the X dimension and then in the Y di-                                                                            |     |

|     | mension to reach their destinations. (b) YX DOR: packets are routed first in the                                                                         |     |

|     | Y dimension and then in the X dimension. (c) O1TURN [7] combines XY DOR                                                                                  |     |

|     | and YX DOR: the first dimension of traversal is chosen randomly. (d) LEF: a                                                                              |     |

|     | packet is routed in the X dimension first (XY DOR) if the difference of the X                                                                            |     |

|     | coordinates of the source node and the destination node $(\Delta x)$ is greater than the                                                                 |     |

|     | difference of the Y coordinates $(\Delta y)$ ; otherwise, if $\Delta y$ is greater than $\Delta x$ , the                                                 |     |

|     | packet is routed in the Y dimension first (YX DOR); in the case that $\Delta x$ is equal                                                                 |     |

|     | to $\Delta y$ , the first dimension of traversal is chosen randomly like in O1TURN                                                                       | 80  |

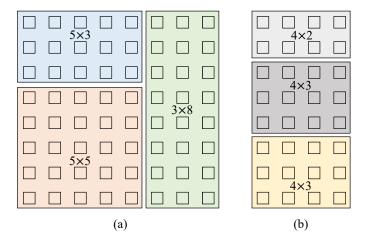

| 5.2 | (a) An example of mapping three parallel applications into an $8\times8$ mesh. (b) An                                                                    |     |

|     | example of mapping three parallel applications into a $4\times8$ mesh                                                                                    | 83  |

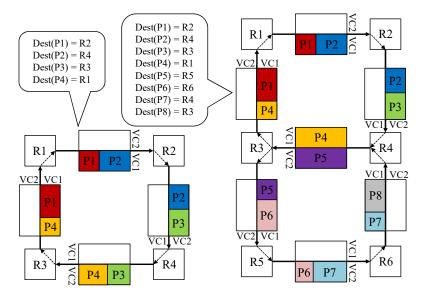

| 5.3 | O1TURN [7] avoids deadlock by completely separating XY packets and YX                                                                                    |     |

|     | packets. In each physical channel, half of the VCs are for XY packets while the                                                                          |     |

|     | other half for YX packets.                                                                                                                               | 85  |

| 5.4 | Two typical deadlock situations that occur when a non-atomic VC allocation                                                                               |     |

|     | policy is used, that is, a VC can be occupied by two or more packets at the same                                                                         |     |

|     | time                                                                                                                                                     | 86  |

| 5.5 | The use of VCs in the proposed deadlock avoidance method. Two design options                                                                             |     |

|     | are provided: (a) <i>Y-restricted</i> and (b) <i>X-restricted</i>                                                                                        | 87  |

| 5.6 | Coordinates of nodes in an m×n mesh                                                                                                                      | 88  |

| 5.7 | The straightforward algorithm for selecting XY DOR and YX DOR described in                                                                               |     |

|     | Section 5.2.1                                                                                                                                            | 91  |

| 5.8  | restricted deadlock avoidance method (Figure 5.5(a)) is used. For the case the  |

|------|---------------------------------------------------------------------------------|

|      | X-restricted deadlock avoidance method (Figure 5.5(b)) is used, lines 5 and 6   |

|      | should be modified as follows: if $\Delta y == 0$ then $R = YX$ DOR             |

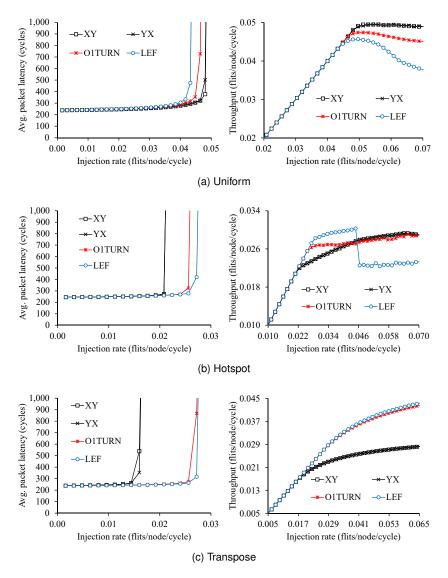

| 5.9  | 8×8 NoC: average packet latency and throughput results with three different     |

|      | traffic patterns                                                                |

| 5.10 | 16×8 NoC: average packet latency and throughput results with two different      |

|      | traffic patterns                                                                |

| 5.11 | 16×16 NoC: average packet latency and throughput results with three different   |

|      | traffic patterns                                                                |

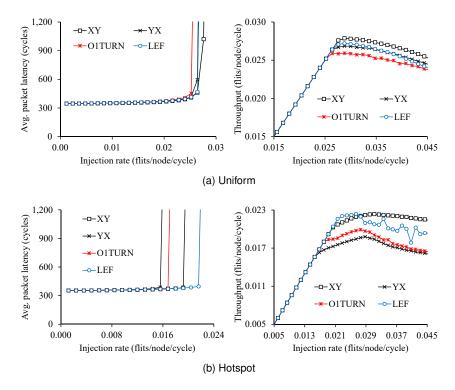

| 5.12 | 64×64 NoC: average packet latency and throughput results with three different   |

|      | traffic patterns                                                                |

| 5.13 | 128×64 NoC: average packet latency and throughput results with two different    |

|      | traffic patterns                                                                |

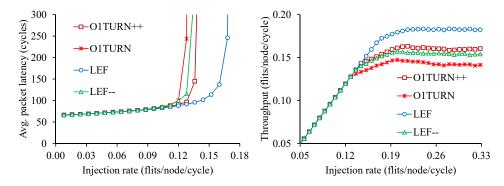

| 5.14 | Comparison of the proposed deadlock avoidance method and the conventional       |

|      | method which is used by O1TURN [7]. In the graphs, O1TURN++ indicates           |

|      | O1TURN with the proposed deadlock avoidance method while LEF indicates          |

|      | LEF with the conventional deadlock avoidance method                             |

| 6.1  | Traffic generator architecture for supporting trace-driven emulation 104        |

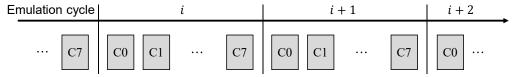

| 6.2  | The TDM scheme for 2D meshes introduced in Chapter 3                            |

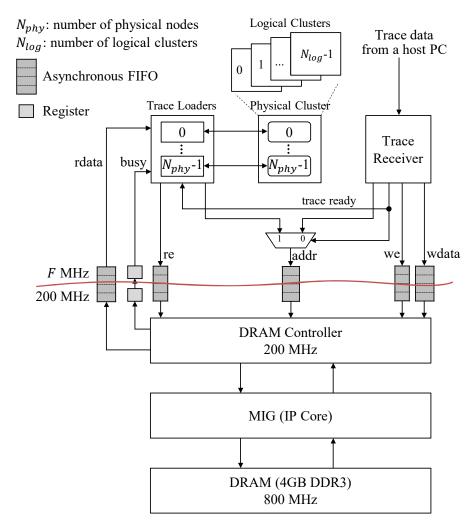

| 6.3  | Overview of the proposed trace-driven emulation architecture on a Xilinx VC707  |

|      | board in which the default 1GB DDR3 DRAM is replaced with a larger one (4GB     |

|      | DDR3 DRAM)                                                                      |

| 6.4  | Datapath surrounding the trace loaders                                          |

| 6.5  | The idea for reducing the number of write ports of the valid memory and the     |

|      | regstatus from two to one                                                       |

| 6.6  | Results obtained when emulating an 8×8 NoC (the parameters are shown in Ta-     |

|      | ble 6.1) with the PARSEC traces                                                 |

| 6.7  | Impact of the method for efficiently implementing the valid and reqstatus mem-  |

|      | ories on the overall FPGA resource requirement and operating frequency 114      |

| 6.8  | Speed of FNoC when emulating the 8×8 NoC which is evaluated in Figure 6.6(a)    |

|      | with the PARSEC traces. The physical cluster size used is 4×4                   |

| 6.9  | Speed of FNoC when emulating the 64×64 NoC which has the same parame-           |

|      | ters as the 8×8 NoC evaluated in Figure 6.6(a) with traces created based on the |

|      | uniform random traffic. The physical cluster size used is 8×4                   |

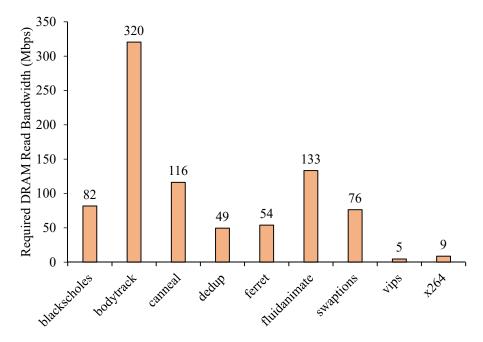

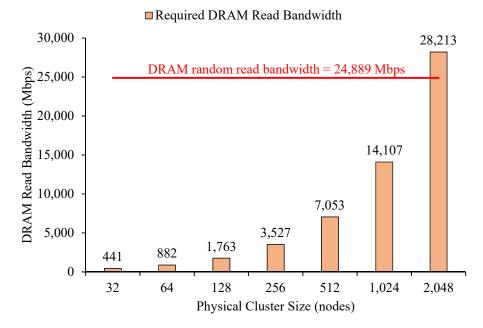

| 6.10 | The DRAM read bandwidth required for an ideal speed $(B_{req})$ when emulating                 |    |

|------|------------------------------------------------------------------------------------------------|----|

|      | the $8\times8$ NoC which is evaluated in Figure 6.6(a) with the PARSEC traces. The             |    |

|      | physical cluster size used is 4×4                                                              | 17 |

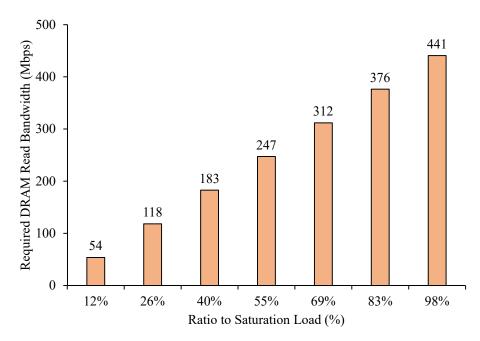

| 6.11 | The DRAM read bandwidth required for an ideal speed $(B_{req})$ when emulating                 |    |

|      | the $64 \times 64$ NoC which has the same parameters as the $8 \times 8$ NoC evaluated in Fig- |    |

|      | ure 6.6(a) with traces created based on the uniform random traffic. The physical               |    |

|      | cluster size used is 8×4                                                                       | 18 |

| 6.12 | Estimation of the required DRAM read bandwidth $B_{req}$ when emulating the                    |    |

|      | $64 \times 64$ NoC mentioned in Figure 6.11 with different physical cluster sizes. Here,       |    |

|      | the traffic load $l$ is 98% of the saturation load. The packet descriptor size $d$ , the       |    |

|      | operating frequency $F$ , and the average packet length $p$ are assumed to be fixed            |    |

|      | when the physical cluster size $N_{phy}$ is changed. The estimation is performed               |    |

|      | using formula (6.2)                                                                            | 19 |

## **List of Tables**

| 2.1 | Comparison of the two network topologies studied in this thesis               |

|-----|-------------------------------------------------------------------------------|

| 2.2 | Comparison of FPGA-based NoC emulators                                        |

| 2.3 | Flit model                                                                    |

| 4.1 | Common parameters of the target NoCs and emulation parameters 69              |

| 4.2 | Individual parameters of each of the target NoCs                              |

| 4.3 | Overhead and speed of emulating each of the target NoCs under uniform and     |

|     | hotspot traffics                                                              |

| 5.1 | Emulation parameters                                                          |

| 6.1 | Parameters of the target NoCs                                                 |

| 6.2 | FPGA resource requirements and operating frequencies when emulating different |

|     | NoC sizes using a cluster of 16 nodes $(4\times4)$                            |

## Chapter 1

## Introduction

#### 1.1 Motivation

#### 1.1.1 The Advent of New Computing Architectures

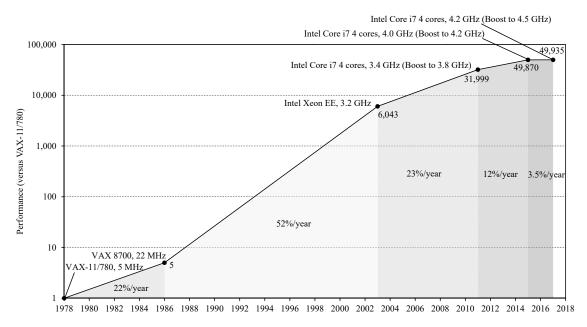

Over the past several decades, the continuous advances in semiconductor process technology according to Moore's Law [8] coupled with Dennard scaling [9] have been a fundamental driver for improving computing performance. Moore's Law states that the number of transistors that can be cost-effectively integrated on a chip doubles every 24 months, which has been achieved by shrinking the transistors. Dennard scaling observes that transistors consume less power and can switch faster as they get smaller. Therefore, after each generation of technology scaling, with the same cost and power budget, computer architects had more transistors which were faster than the previous generation to be able to incorporate new architectural techniques. This resulted in the exponential improvement of integrated circuit performance. For instance, as shown in Figure 1.1, the processor performance was improved 6,043× from 1978 to 2003 with the average annual growth rate of 22% in the first six years and 52% in the remaining years.

However, recent trends have made it harder to continue to scale computing performance in the conventional way. Dennard scaling has broken down since the middle of the 2000s because the current leakage has become a serious problem as the transistor size decreases. Moore's Law is also reaching its limit. This slowdown in technology scaling is leading to serious consequences. As shown in Figure 1.1, the average annual growth rate of processor performance from 2003 to 2011 was 23% compared to 52% in the previous 17 years. It is further decelerated to 12% in the period from 2011 to 2015 and just 3.5% in recent years.

Nevertheless, the need for computing performance improvement is becoming higher and higher. New technologies like social networking services and Internet of Things devices are resulting in the ever-increasing volume of data that need to be processed. Techniques making use of these data for creating new values such as deep learning [10] also require tremendous

Figure 1.1: Growth in processor performance from 1978 to 2017 (Figure adapted from [1]). The data are collected by running the SPEC integer benchmarks [2] and normalized to the performance of the VAX-11/780 [3].

computing power. Apart from that, many large problems in science and engineering can only be solved if we have much more computational resources than at this time.

In response to the impending end of the benefits of technology scaling and the pressing need for more computing power, we need significant innovation in computing architecture. Two complementary approaches have been shown to be effective: increasing the number of processing elements on a chip and domain/application-specific specialization. Using these approaches, three different types of hardware platforms have been developed: multi/many-core processors, MultiProcessor Systems-on-Chip (MPSoCs), and hardware accelerators.

The microprocessor industry has shifted to integrating multiple processor cores on a chip since the middle of the 2000s. Most processors used in smartphones and personal computers today are multi-core processors with two to around ten cores. Many-core processors with more number of cores have also been developed for use in larger-scale systems like supercomputers and datacenters. For instance, the Intel Xeon Phi Knights Landing many-core processor [11] released in 2016 has up to 72 cores. Sunway TaihuLight, the world's fastest supercomputer as of November 2017, is based on a many-core processor with 260 cores [12]. To achieve higher performance and better power efficiency, many-core processors with more and more cores are being studied at present.

MPSoCs [13] are Systems-on-Chip (SoCs) which have been designed for embedded applications in various domains such as communications, multimedia, networking, and signal processing. An MPSoC often contains a collection of processing elements of multiple types (general-

purpose processor cores or domain-specific processing units) which communicate and cooperate to perform the execution of tasks of the target application. Like general-purpose many-core processors, to achieve higher performance, better power efficiency and meet the increasingly stringent requirements of target applications, modern MPSoCs are growing in complexity with more and more processing elements.

Accelerators are hardware units specialized for specific computational tasks. The use of accelerators started in the 1980s with the deployment of floating-point co-processors. Accelerators have also been adopted in designing SoCs including MPSoCs. However, the wide adoption of accelerators in different types of computing systems has not been started until very recently when the slowdown in technology scaling made it hard to meet the increasingly high demand for computing power. There have been numerous accelerators proposed recently for speeding up different tasks in machine learning, databases, graph processing, networking processing, and a variety of other applications [14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31, 32, 33, 34, 35]. Some have even been deployed in commercial systems like Google Tensor Processing Unit [14] and Microsoft's FPGA accelerators [15, 17, 16]. Like in MPSoCs, many accelerators are comprised of multiple processing elements interacting with each other, and they are growing in complexity.

#### 1.1.2 Interconnection Problems

As presented in Section 1.1.1, modern many-core processors, MPSoCs, and many hardware accelerators are composed of multiple processing elements that communicate and cooperate with each other when executing a task. The processing elements also interact with the other components of the system such as the memory and input/output (I/O) modules. The latency and bandwidth of the interconnection between these components are highly critical to the overall performance, especially when the number of components is large.

#### 1.1.2.1 Problems of Traditional On-Chip Interconnection Architectures

The simplest way to connect a set of components together is to use a bus. A key property of buses is *broadcast*: a message transmitted by a node over the bus is received by all other nodes. Also, only one node can be the transmitter at any given time. With these properties, buses have been widely used as the interconnects of small-scale multi-core processors, MPSoCs, and hardware accelerators because of their simplicity and effectiveness. However, as the number of components that need to be interconnected increases, it is hard to make the bus operate at a high speed. Moreover, it is hard to provide enough communications bandwidth since only one message can be sent over the bus at any given time.

Point-to-point interconnects have been used in cases that the required communications band-

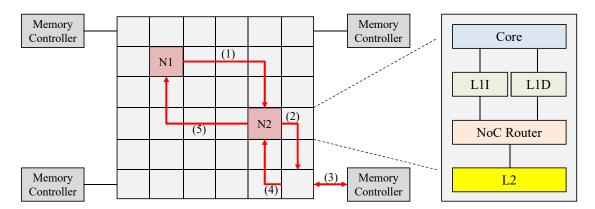

Figure 1.2: An example of a many-core processor architecture with 2D-mesh-based NoC.

width is higher than what a bus can provide. In a point-to-point interconnect, there is a direct link between any pair of nodes. Thus, a high communications bandwidth can be achieved since the transmission between a pair of nodes is not affected by other pairs. However, as the number of components that need to be interconnected increases, the implementation costs (hardware and power requirements) of point-to-point interconnects become prohibitive.

Crossbars are other alternatives to address the communications bandwidth problem of buses. Compared to point-to-point interconnects, the implementation costs of crossbars are cheaper. However, they are still too high when the number of interconnected components is large. Specifically, the cost of a crossbar grows quadratically with the number of I/O ports.

In summary, all of the traditional on-chip interconnection architectures are not scalable. They cannot keep pace with the number of components that need to be interconnected. Therefore, a new class of on-chip interconnects called Networks-on-Chip (NoCs) has been developed [36, 4, 37, 38].

#### 1.1.2.2 Network-on-Chip (NoC)

It has been shown that NoCs can address both the communications performance and implementation cost problems of the traditional on-chip interconnection architectures. They thus have been used as the interconnects of most of modern many-core processors, MPSoCs, and many hardware accelerators [11, 39, 40, 41, 42, 43, 44, 45, 46, 47, 48, 49, 50, 51, 18, 23, 24, 25, 26, 20, 31].

A NoC is composed of a collection of routers interconnected with each other according to a predetermined topology. To explain how a NoC can be integrated into a system, let us look at an example below.

Figure 1.2 shows an example of a many-core processor architecture with two-dimensional (2D)-mesh-based NoC. This architecture is close to the recently released Intel Xeon Phi Knights Landing [11] and OpenPiton [40, 41] architectures. Each node contains a processor core, a private L1 cache (separated into L1I and L1D), a bank of L2 cache, and a NoC router. The

routers of two adjacent nodes are interconnected to each other. L2 is a shared cache and is divided into banks that are distributed among nodes. The organization of L2 is assumed to be Statically-mapped Non-Uniform Cache Architecture (S-NUCA). Specifically, the mapping of data into L2 banks is pre-determined, based on their physical addresses. Figure 1.2 shows how handling an L1 miss at node N1 involves the use of the NoC. Here we assume that the home L2 bank of the data requested is in node N2. The handling steps are as follows. First, a miss request is sent from node N1 to node N2 (step (1)). If hit in the home L2 bank at node N2, then the data are sent back to the L1 cache at node N1 (step (5)). Otherwise, an L2 miss request is sent to the target memory controller (steps (2) and (3)). The memory controller loads the requested data and sends back to the home L2 bank (step (4)). Finally, the data are sent back to the L1 cache from the home L2 bank (step (5)). The request/response messages between node N1, node N2, and the memory controller are transmitted over the NoC.

#### 1.1.3 Challenges in NoC Design

The example in Figure 1.2 described in Section 1.1.2.2 suggests that the NoC performance is highly critical to the overall performance. In [52], Sanchez *et al.* quantitatively show that, in a many-core processor with 128 multithreaded cores, the NoC is responsible for 60% to 75% of the miss latency and thus has a significant impact on the overall performance. The authors also find that improving the NoC can help to boost the overall performance by up to 20% and that the impact of the NoC becomes more pronounced as the number of cores increases. Therefore, research and development of NoCs play a key role in designing future large-scale architectures with hundreds to thousands of cores.

However, a major obstacle to research and development of large-scale NoCs is the lack of fast modeling methodologies that can provide a high degree of accuracy. Analytical models like those proposed in [53, 54] are extremely fast but may incur significant inaccuracy in many cases. Thus, NoC designers often rely on simulation, which can provide much more accurate evaluation results and insights into the designs, to test their ideas and make design decisions.

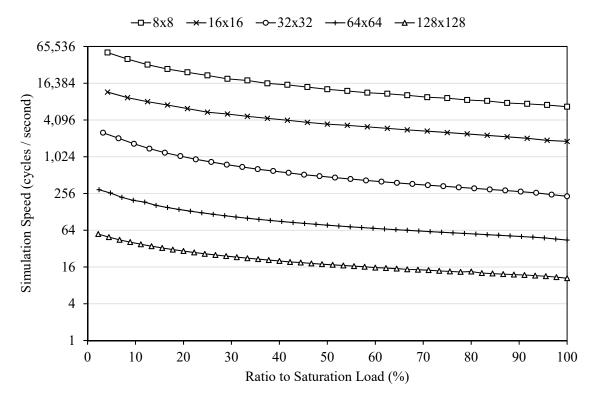

Software simulators including full-system simulators such as gem5 [55] and stand-alone NoC simulators such as BookSim [5] have been widely used in the NoC research community. Although these simulators offer various advantages such as the flexibility and the broad range of programming tools, they suffer from two serious drawbacks. First, it is hard to validate a complex design because various types of errors may be introduced during specifying, abstracting, and implementing certain details [56]. One can design and implement a feature in a way that would be impractical to implement in hardware. Second, and more important, the simulators are too slow to simulate large-scale designs with hundreds to thousands of nodes in a reasonable time. Sanchez *et al.* [57] mentioned that it would take almost a year for gem5 to simulate

1s of a thousand-core chip. Compared to full-system simulators, stand-alone NoC simulators, which often support much more detailed NoC models, are faster, but simulating a large-scale NoC still requires an excessive amount of time. Because of this, most previous studies are limited to NoCs with around 100 nodes. To investigate novel designs with hundreds to thousands of nodes, it is crucial to improve the simulation speed while maintaining the simulation accuracy. Unfortunately, using existing parallelization techniques to improve the simulation speed without sacrificing the simulation accuracy is hard [58].

To address the simulation speed problem, there have been some attempts to build NoC emulators using Field-Programmable Gate Arrays (FPGAs) [59, 60, 61, 62, 63, 64, 65, 66, 67, 68]. However, these NoC emulators suffer from the scalability problem. They cannot scale to large NoCs due to the FPGA logic and memory constraints.

A recent study [69] has shown that even an extremely large FPGA does not have enough logic blocks to fit a moderately complex NoC design of around 150 nodes. Some prior studies simplify the router models and sacrifice the cycle accuracy, a level of emulation accuracy in which target NoCs are emulated on a cycle-by-cycle basis, to reduce the number of required logic blocks. For instance, DART [65] uses a simple single-stage NoC router with only one output channel to model some multi-stage pipelined NoC routers with five output ports. However, Khan [70] has shown empirical evidence that using a simplified emulation model or sacrificing the cycle accuracy may lead to conclusions that are wrong both quantitatively and qualitatively. Thus, it is necessary to preserve both of them.

Besides the challenge of a large number of required logic blocks, emulating a large-scale NoC also requires a large amount of memory for modeling of traffic workloads. However, the on-chip memory capacity of an FPGA is very small, at most from several to around only ten megabytes. Off-chip memory (usually DRAM) has a larger capacity but is much slower than on-chip memory. The use of off-chip memory may substantially degrade the emulation speed.

There are two types of workloads used in NoC emulation: synthetic workloads and trace-driven workloads. Synthetic workloads are those based on mathematical modeling of common traffic patterns in real applications. They have a high degree of flexibility and are easy to create. A set of carefully designed synthetic workloads can provide a relatively thorough coverage of the characteristics of the target NoCs. It has also been shown that evaluation on synthetic workloads is indispensable in many cases. For instance, when designing a routing algorithm, the use of synthetic workloads is mandatory for assessing the algorithm on possible corner cases like those under extremely high loads. On the other hand, trace-driven workloads are those based on trace data captured from either a working system or an execution-driven simulation/emulation. They are effective for evaluating target NoCs under the intended applications.

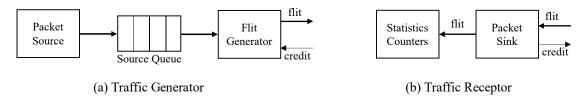

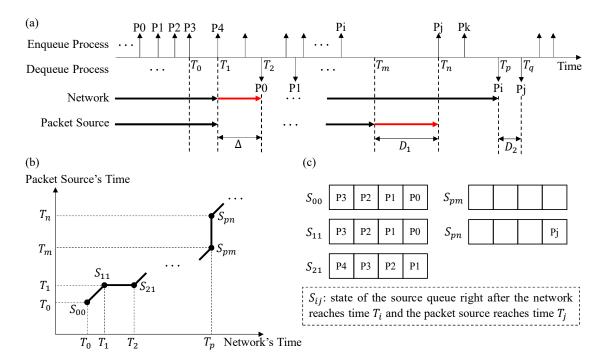

To evaluate a NoC on a synthetic workload, it is necessary to use *open-loop measurements* [4] in which a large FIFO buffer called *source queue* is placed after each packet source to de-

couple the traffic generation and injection process from the NoC. If the source queues are not large enough, then the traffic generation and injection process will be affected by the NoC, and therefore the workload produced by the traffic generators will not be the one originally specified. Because of this, emulating large-scale NoCs under synthetic workloads on FPGAs requires a large amount of memory. Although off-chip memory can be used, the emulation speed may be degraded substantially since accessing off-chip memory takes much more time than on-chip memory.

In the case of emulation with trace-driven workloads, trace data are often much larger than the total capacity of FPGA on-chip memory and thus must be stored in off-chip memory. Most of the existing FPGA-based NoC emulators simplify the control of loading trace data from the off-chip memory, generating messages based on the loaded trace data, and injecting the messages to the NoC by using soft processors like Microblaze or hard processors on SoC FPGAs. The processors are also responsible for manipulating the emulation and making sure that there is no timing error. This approach makes the implementation easy but the emulation speed is drastically reduced with increasing the NoC size [68].

#### 1.2 Thesis Contributions

This thesis proposes methods to overcome the challenges in the FPGA emulation approach described in Section 1.1.3, thereby enabling fast and accurate modeling of NoCs with hundreds to thousands of nodes. While the goal of these methods is to enable fast and accurate modeling of large-scale NoCs, they are also beneficial to the modeling of current NoCs with tens to around 100 nodes.

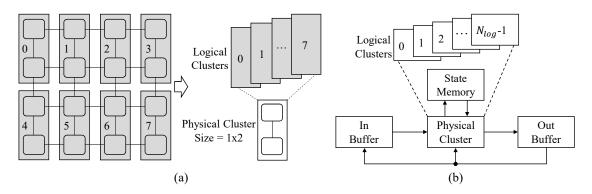

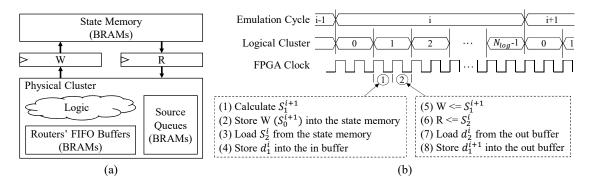

Novel time-division multiplexing methods for NoC emulation: The thesis proposes a novel use of time-division multiplexing (TDM) where the emulation cycle is decoupled from the FPGA cycle and a network is emulated by time-multiplexing a small number of nodes. This approach helps to overcome the FPGA logic constraints, thereby enabling emulation of large-scale NoCs with hundreds to thousands of nodes using a single FPGA. Although the TDM technique has been adopted in some prior work [60, 63, 65, 67, 68], it has not been discussed thoroughly. The implementation methods in these studies are not scalable in terms of both FPGA logic requirements and emulation speed. Moreover, they consider only some typical direct networks including 2D meshes, 3D tori, hypercubes, and fully connected networks. These direct networks have regular physical arrangements that are intuitively matched to Very-Large-Scale Integration (VLSI) packaging constraints and thus have been employed in many practical systems. On the other hand, indirect networks such as fat-trees have an attractive feature of lower hop counts that imply lower packet transmission delay and have also been widely adopted. Thus, it is highly desirable that indirect network topologies be supported. However, since the connectivity pattern of nodes in

an indirect network is generally much more complicated than that in a direct network, using the TDM technique to emulate indirect networks is not trivial. This thesis discusses in detail methods for efficiently applying the TDM technique for both direct and indirect network topologies with the focus on 2D meshes and fat-trees (k-ary n-trees). Because these two network topologies are the bases of almost all actually constructed network topologies [4], it can be expected that the proposed methods can be extended for a wide range of networks.

While the proposed TDM methods enable the emulation of large-scale NoCs, they alone are not sufficient. To achieve a high emulation speed, it is essential to address the memory constraints caused by modeling traffic workloads.

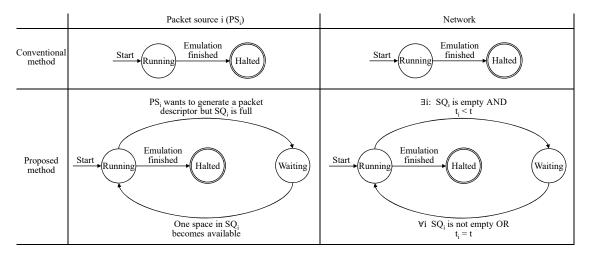

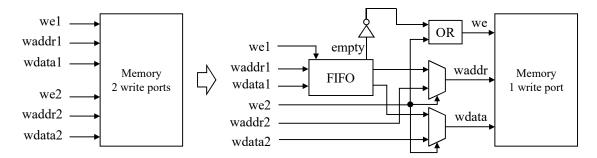

An efficient method for modeling of synthetic workloads: Currently, due to the lack of trace data of large-scale NoC-based systems, using synthetic workloads is practically the only feasible approach for emulating large-scale NoCs with thousands of nodes. The thesis describes how to emulate a NoC under a synthetic workload without requiring a large amount of memory by (1) decoupling the time counter of each packet source from that of the network and (2) properly allowing the network to operate interactively with the packet sources based on the status of the source queues and the relationship between the time counters. This approach makes the emulation take place as if infinite source queues could be used at the expense of stalling the network in some cases. Although the emulation is slowed down in cases of stalling the network, the memory footprint of the emulation is bounded regardless of the offered traffic load. Thus, we can use only FPGA on-chip memory to implement the source queues even when emulating large-scale NoCs. The thesis also presents methods to minimize the number of times the network is stalled.

**FNoC – An emulator for NoC emulation under synthetic workloads**: Using the proposed time-multiplexed emulation methods and the method for modeling of synthetic workloads, the thesis develops a NoC emulator, called FNoC, on a Virtex-7 XC7VX485T FPGA. The main evaluation results are as follows:

- The size of the largest NoC that can be emulated by FNoC depends on only the on-chip memory capacity of the FPGA used. The thesis demonstrates the emulations of NoCs of various sizes, up to 128×128 (16,384 nodes) for the 2D mesh topology and 4-ary 6-tree (6,144 switch nodes and 4,096 terminal nodes) for the fat-tree topology.

- When emulating a 128×128 NoC and a 4-ary 6-tree NoC under a synthetic workload, FNoC is, respectively, 5,047× and 232× faster than BookSim [5], one of the most widely used software-based NoC simulators.

- Extensive experimentation shows that FNoC and BookSim report exactly the same results in every case. This indicates that the NoCs modeled by FNoC are totally identical to those of BookSim.

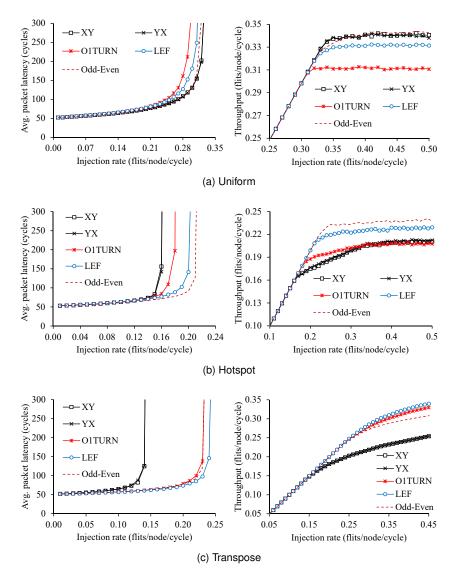

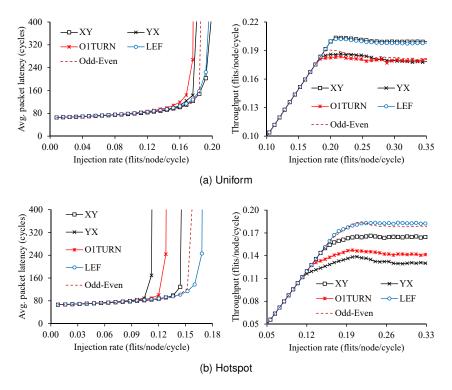

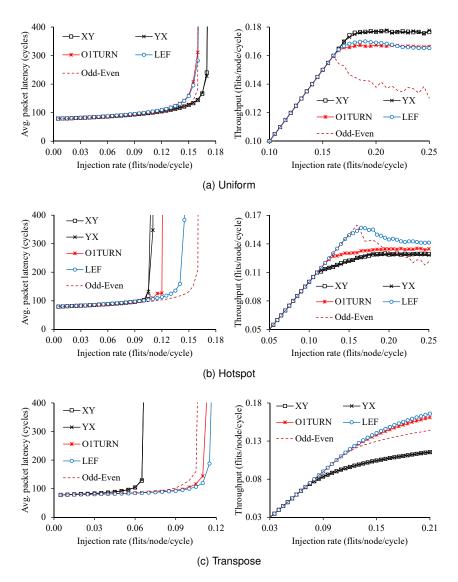

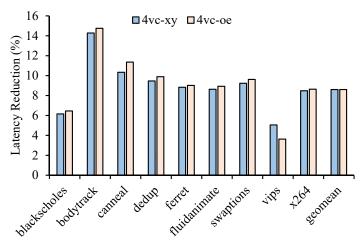

A use case of FNoC in design and modeling of a new routing algorithm: The thesis shows the usability of FNoC by designing and modeling an effective routing algorithm, called LEF, for 2D mesh NoCs and evaluating it for various network sizes, from 8×8 to 128×64. LEF is developed based on the idea which is originally proposed in [71]. LEF has an oblivious routing scheme and thus a low design complexity. It, however, can achieve high performance by properly distributing the load over two network dimensions and using an efficient deadlock avoidance method. Because of the lack of fast modeling methodologies that can provide a high degree of accuracy, most existing routing algorithms have been evaluated in NoCs of limited size. FNoC enables the evaluation in large-scale NoCs with thousands of nodes in a practical time. LEF is evaluated against O1TURN [7], one of the best oblivious routing algorithms for 2D meshes, and a complicated adaptive routing algorithm based on the odd-even turn model [72]. The evaluation results show that, in an 8×8 NoC, LEF provides 3.6%-10% higher throughput than O1TURN and comparable performance to the adaptive routing algorithm under three different traffic patterns. LEF is particularly effective when the network is asymmetric. In a  $16\times8$  NoC, LEF outperforms the adaptive routing algorithm and delivers up to 28.3% higher throughput than O1TURN. However, as the NoC size increases, the performance of the algorithms is strongly affected by the resource allocation policy in the network and the effects are different for each algorithm. This result would not be obtained if modeling of large-scale NoCs could not be performed.

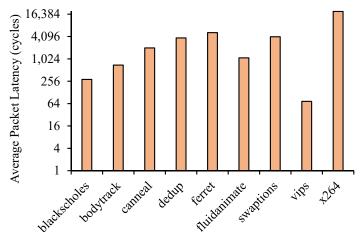

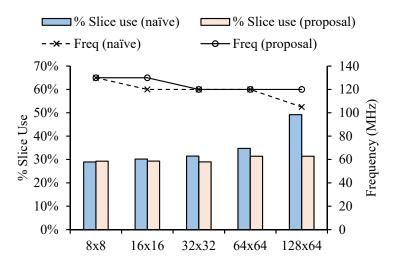

Towards NoC emulation under future scenarios with trace-driven workloads: While synthetic workloads can provide a relatively thorough coverage of the characteristics of the emulated NoCs, evaluation on trace-driven workloads is still required in some cases such as assessing some application-specific optimizations. The thesis takes this into account and extends FNoC to support trace-driven emulation which will be useful for research and development of large-scale NoCs in the future when trace data of large-scale NoC-based systems are available. Since trace data are large, they must be stored in off-chip memory. The thesis proposes an effective trace data loading architecture which does not include processors for speeding up trace-driven emulation of NoCs with up to thousands of nodes. The thesis also introduces some methods to effectively hide the off-chip memory access time and improve the scalability of the emulation architecture in terms of operating frequency and FPGA resource requirements. These proposals are tightly coupled to the time-multiplexed emulation methods. The evaluation results show that the extended NoC emulator achieves a speedup of 260× compared to BookSim when emulating an 8×8 NoC with the PARSEC traces [73] collected by Hestness et al. [74] while also providing the same results; and the speedup is increased to 5,106× when emulating a 64×64 NoC with trace data created based on a synthetic workload.

The work in this thesis contributes directly to the formation of infrastructures for research and development of large-scale NoCs, which is crucial for developing more powerful and efficient many-core processors, MPSoCs, and hardware accelerators in the future.

#### 1.3 Thesis Organization

The rest of this thesis is organized as follows.

Chapter 2 provides relevant background in NoC, FPGA, and NoC modeling. This chapter also reviews the efforts that have been made over the years in NoC modeling by both software simulation and FPGA emulation and discusses the approach of the thesis. The chapter ends by presenting the NoC emulation model adopted in the thesis.

Chapter 3 proposes novel time-division multiplexing methods to overcome the FPGA logic constraints, thereby enabling emulation of large-scale NoCs with hundreds to thousands of nodes using a single FPGA. The chapter discusses in detail architectures and methods for supporting both direct and indirect network topologies with the focus on 2D meshes and fat-trees (*k*-ary *n*-trees). The chapter also describes the basic rules for writing time-multiplexed emulation Register-Transfer Level (RTL) code. The content of this chapter is largely based on the author's published work [75, 76, 77, 78].

Chapter 4 proposes a method for addressing the memory constraints in modeling synthetic workloads that are presently the only feasible workloads for emulating large-scale NoCs with thousands of nodes. The proposed method reduces the amount of required memory so that it is not necessary to use off-chip memory even when emulating NoCs with thousands of nodes. This not only makes the overall design much simpler but also significantly contributes to the improvement of emulation speed since the use of slow off-chip memory is avoided. The chapter also presents a NoC emulator that is built based on the combination of the method for modeling of synthetic workloads and the time-multiplexed emulation methods proposed in Chapter 3. The content of this chapter is largely based on the author's published work [76, 77, 78].

Chapter 5 shows the usability of the NoC emulator proposed in Chapter 4 by designing and modeling an effective routing algorithm for 2D mesh NoCs and evaluating it for various network sizes, from  $8\times8$  to  $128\times64$ . The content of this chapter is largely based on the author's published work [79].

Chapter 6 extends the NoC emulator proposed in Chapter 4 to support trace-driven emulation which will be useful for research and development of large-scale NoCs in the future when trace data of large-scale NoC-based systems are available. The chapter proposes an effective trace data loading architecture and some methods to hide the off-chip memory access time and improve the scalability of the emulation architecture in terms of operating frequency and FPGA resource requirements. These proposals are tightly coupled to the time-multiplexed emulation methods introduced in Chapter 3. The chapter also presents the evaluation of the extended NoC emulator. The content of this chapter is largely based on the author's published work [80].

Chapter 7 summarizes the thesis and discusses the future work.

## **Chapter 2**

## **Background and Related Work**

#### 2.1 NoC Basics

Any NoC architecture can be characterized by four properties: topology, routing, flow control, and router architecture [4, 38]. In this thesis, the components that are interconnected by a NoC in a many-core system (many-core processor, MPSoC, or hardware accelerator) are collectively called *cores*. A core can be a processing element, a memory module, or an I/O module.

#### 2.1.1 Topology

Topology defines how channels and nodes are arranged in a network. Because topology heavily affects the design of the other properties, choosing a topology is usually the first step in designing a NoC. The topology establishes an optimal bound on performance, that is, throughput and latency, of a network. The routing algorithm, flow control protocol, and router architecture determine how closely the optimal performance bound can be approached.

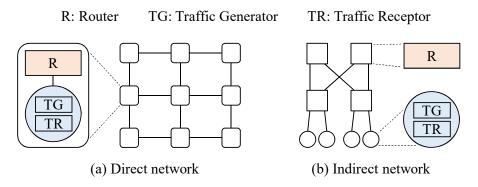

Direct network topology versus indirect network topology: In direct networks such as meshes and tori, each node behaves as both a terminal node and a switch node and thus is composed of a core connected with a router. On the other hand, indirect networks such as butterflies (e.g., flattened butterfly [81]) and trees (e.g., fat-tree [82], Fat H-Tree [83]) distinguish between terminal node and switch node. Specifically, each terminal node in an indirect network is a core while each switch node is a router.

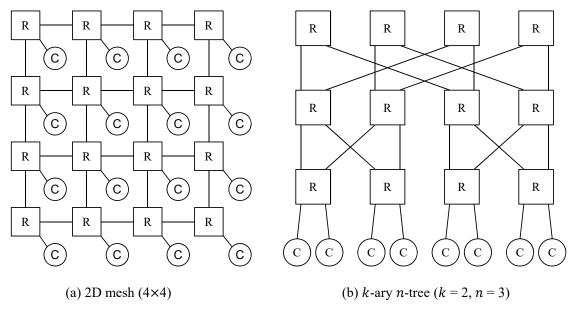

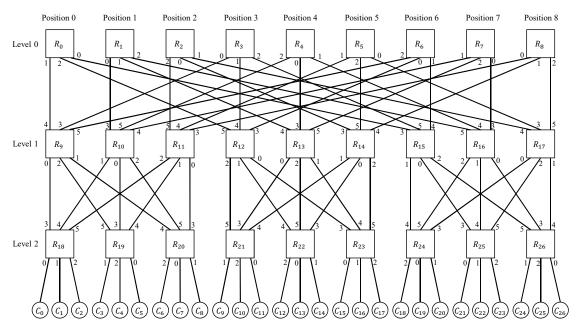

This thesis studies two network topologies: 2D mesh and k-ary n-tree (a commonly used topology in the fat-tree family). Figure 2.1 illustrates the position of routers, cores, and links between routers in each topology. Table 2.1 provides a comparison of the two topologies for three key metrics. The router radix here is defined as the number of ports per router. It can be used as an indicator of the cost of a network. In general, a network with higher router radix is more expensive to implement because it requires more area and energy at each router.

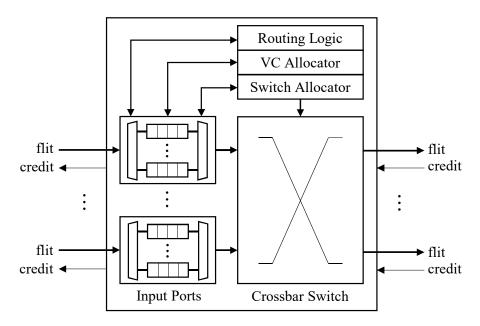

Figure 2.1: The position of routers (R), cores (C), and links between routers in each of the two network topologies studied in this thesis.

Table 2.1: Comparison of the two network topologies studied in this thesis

|                        | Туре                      | #cores | #routers   | Router radix <sup>(1)</sup> |

|------------------------|---------------------------|--------|------------|-----------------------------|

| 2D mesh $(x \times y)$ | Direct network topology   | xy     | xy         | 5 <sup>(2)</sup>            |

| k-ary n-tree           | Indirect network topology | $k^n$  | $nk^{n-1}$ | $2k^{(3)}$                  |

<sup>(1):</sup> the number of ports per router.

An  $x \times y$  2D mesh network comprises xy nodes, each has one core and one radix-5 router<sup>1</sup>. Note that some ports of the routers at the edge of the mesh are not used. These routers can be simplified and thus require less area and energy than the others.

A k-ary n-tree consists of  $k^n$  cores (terminal nodes) and n levels of  $k^{n-1}$  routers (switch nodes). The router radix in this network is 2k. Thus, when  $k \geq 3$ , the cost for implementing each router in this network is higher than in 2D mesh networks. Also, note that some ports of the routers at the root of the tree are not used.

#### **2.1.2** Routing

With the roadmap determined by the topology, routing algorithms define which path a packet takes to reach its destination. A routing algorithm can be categorized as oblivious or adaptive depending on how the routing decisions are determined.

<sup>(2):</sup> some ports of the routers at the edge are not used.

<sup>(3):</sup> some ports of the routers at the root of the tree are not used.

<sup>&</sup>lt;sup>1</sup>This thesis considers the common case that there is only one core in each node of a 2D mesh network. In general, a designer might choose to put c cores ( $c \ge 2$ ) into each node; in this case, the router radix of the network is 4 + c.

Oblivious routing algorithms do not use the network's state information in their routing decisions. For example, in 2D mesh networks, a widely used oblivious routing algorithm is the XY dimension-order routing (DOR) algorithm where a packet is routed first in the X dimension and then in the Y dimension to reach its destination. Although this algorithm may produce load imbalance for some traffic patterns, it has been widely used in many commercial and research systems [11, 43, 84, 40, 41] because it is very simple to implement, has short routing delay, requires low hardware overhead, and simplifies the deadlock avoidance problem.

Contrary to oblivious routing algorithms, adaptive routing algorithms consider the network's state information in their routing decisions. Thus, they can adapt to the condition of the network and are often better than oblivious routing algorithms in load balancing. However, adaptive routing algorithms are generally more complex, have longer routing delays, and incur more hardware overhead.

Apart from the requirements of routing delay and hardware overhead, deadlock freedom is an issue that must be taken into account when designing any routing algorithm. A deadlock occurs when multiple packets form a dependency cycle that lasts forever, that is, there is no way that this cycle can be broken. In general, deadlock freedom can be achieved by focusing on the routing algorithm or the flow control protocol.